La fuga di notizie su AMD Zen 7 'Florence' fa pensare a chip Epyc a 288 core e a importanti guadagni di efficienza per i computer portatili

La piattaforma server di prossima generazione di AMD potrebbe spingere i conteggi dei core mainstream in un territorio impensabile solo pochi anni fa, con gli utenti di workstation e desktop di fascia alta potenzialmente destinati a beneficiare degli stessi blocchi di costruzione.

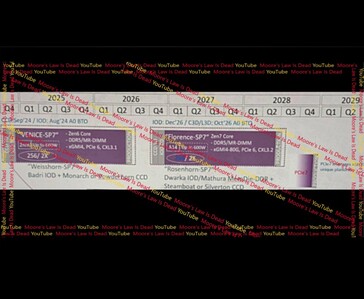

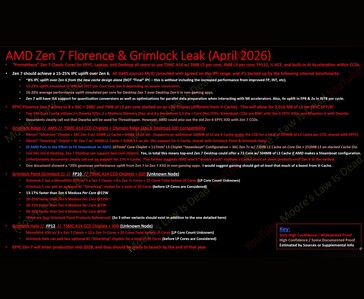

Secondo una serie di diapositive condivise da Tom, noto leaker di hardware e conduttore di Moore's Law Is Dead su YouTube, L'ammiraglia Zen 7 EPYC di AMDcon il nome in codice Florence, si basa su due die di I/O "Dwarka" e due die di memoria "Mathura", che prendono entrambi il nome da antiche città indiane di notevole importanza storica e spirituale, abbinati a un massimo di otto CCD Steamboat a 36 core, per un totale di 288 core per socket.

Ogni CCD Steamboat combina un Zen 7 core sul nodo Nodo A14 di TSMC con un chiplet di cache L3 separato su N4P, impilato sotto anziché sopra come con la 3D V-Cache esistente. Le diapositive riportano 7 MB di L3 per core, un'interfaccia PCIe 6 + CXL 3.2, una velocità di collegamento xGMI4-80G e un TDP fino a 600 W.

I nostri Top 10

» Top 10 Portatili Multimedia

» Top 10 Portatili Gaming

» Top 10 Portatili Gaming Leggeri

» Top 10 Portatili da Ufficio e Business economici

» Top 10 Portatili Premium da Ufficio/Business

» Top 10 Portatili sotto i 300 Euro

» Top 10 Portatili sotto i 500 Euro

» Top 10 dei Portatili Workstation

» Top 10 Subnotebooks

» Top 10 Ultrabooks

» Top 10 Convertibili

» Top 10 Tablets

» Top 10 Tablets Windows

» Top 10 Smartphones

Sia il die IO di Dwarka che il die di memoria di Mathura sono indicati per l'uso di Il processo N3C di TSMC. Una diapositiva mostra un tape-out A0 previsto per ottobre 2026, con una produzione mirata per la metà del 2028 e un lancio intorno alla fine dello stesso anno. Una voce separata della roadmap indica l'arrivo di una piattaforma PCIe Gen 7 intorno al 2029, forse come aggiornamento di metà generazione su un nuovo socket.

Gli acquirenti di piattaforme AMD di attuale generazione potrebbero non dover cambiare socket per beneficiare del prossimo salto architettonico, e gli utenti di computer portatili in particolare potrebbero vedere alcuni dei maggiori guadagni. I documenti trapelati indicano che i CCD Zen 7 sono retrocompatibili con i die IO Kedar e Weisshorn di precedente generazione, mentre i CCD Silverton funzioneranno con gli IOD Badri, Kedar, Puri e Dwarka attraverso le confezioni SP7 e SP8, con supporto per 2, 4, 6 o 8 CCD per socket. Threadripper e HEDT tramite l'IOD Dwarka è esplicitamente indicato.

Una tabella delle prestazioni separata per i chiplet Silverton e Silverking, orientati al consumatore, elenca guadagni per core dal 16 al 20 percento con carichi di lavoro server inferiori a 9 W e dal 30 al 36 percento in scenari APU client da 3 W/core, indicando miglioramenti di efficienza particolarmente forti per i laptop sottili e leggeri.

Tom ipotizza che la larghezza simile del CCD Steamboat a 36 core rispetto al Silverton a 16 core potrebbe teoricamente consentire ad AMD di inserire due Steamboat su AM5 per un chip desktop a 72 core, sebbene nessuna diapositiva trapelata confermi tale prodotto. Lo stesso leaker suggerisce che qualsiasi componente di questo tipo sarebbe più probabilmente destinato ai clienti embedded che al mercato DIY.

Guardi il suo video, linkato qui sotto, per uno sguardo dettagliato alle informazioni trapelate e alla sua opinione in merito.