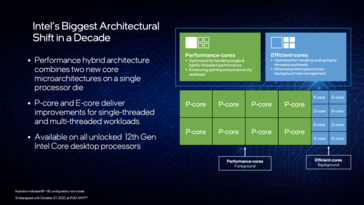

Doponumerosi giri di fughe di notizieè finalmente arrivato. Intel ha tolto le protezioni dalla nuova linea di processori Alder Lake-S di 12a generazione per i desktop. Durante la presentazione, Marcus Kennedy di Intel ha offerto una panoramica di ciò che rende Alder Lake tick e come l'architettura eterogenea composta da Golden Cove Performance (P)-cores e Gracemont Efficiency (E)-cores lavorare nel sistema.

I nostri Top 10

» Top 10 Portatili Multimedia

» Top 10 Portatili Gaming

» Top 10 Portatili Gaming Leggeri

» Top 10 Portatili da Ufficio e Business economici

» Top 10 Portatili Premium da Ufficio/Business

» Top 10 Portatili sotto i 300 Euro

» Top 10 Portatili sotto i 500 Euro

» Top 10 dei Portatili Workstation

» Top 10 Subnotebooks

» Top 10 Ultrabooks

» Top 10 Convertibili

» Top 10 Tablets

» Top 10 Tablets Windows

» Top 10 Smartphones

ISA eterogenea, ora sul desktop mainstream

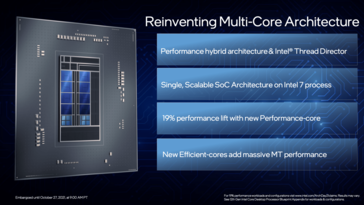

Intel dice che i P-cores sono ottimizzati per applicazioni a thread singolo e leggero come giochi e attività di produttività generale in primo piano, mentre gli E-cores sono orientati verso carichi di lavoro con molti thread. Gli E-cores possono anche aiutare a gestire le attività in background, mentre i P-cores si concentrano maggiormente sugli aspetti delle prestazioni. Questo non è troppo diverso dall'approccio big.LITTLE che i processori ARM hanno avuto per anni.

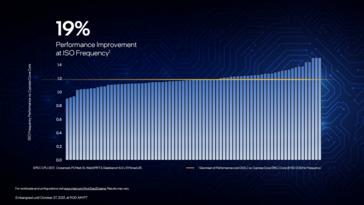

Intel ha detto che questo cambio di architettura può offrire fino al 19% di miglioramento rispetto alla precedente generazione di core Cypress Cove in Rocket Lake alla stessa frequenza.

Direttore dei filetti Intel

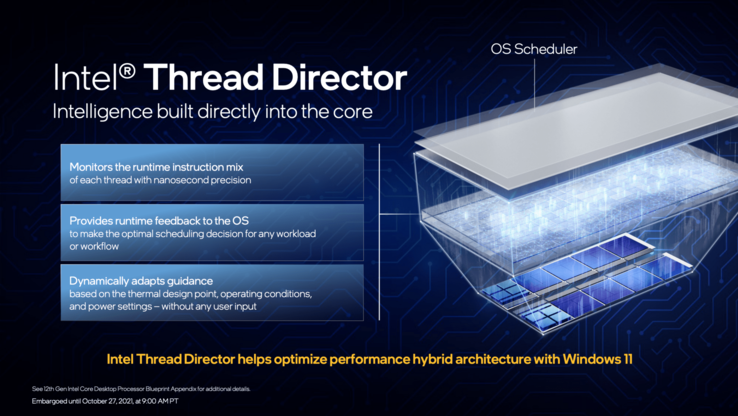

Mentre i sistemi operativi mobili sono costruiti da zero per essere consapevoli delle architetture eterogenee, la situazione è diversa su un desktop. Pertanto, Intel ha costruito il proprio modo di indirizzare i thread al core pertinente

Chiamato Intel Thread Director, questo permette allo scheduler del sistema operativo di essere consapevole della presenza di diverse ISA sullo stesso SoC e gestire efficacemente le risorse. Intel ha detto che Thread Director prende in considerazione diversi parametri come TDP, potenza disponibile, ecc. e fornisce un feedback continuo allo scheduler OS con "precisione al nanosecondo".

Cache L3 comune da 30 MB per P-cores ed E-cores

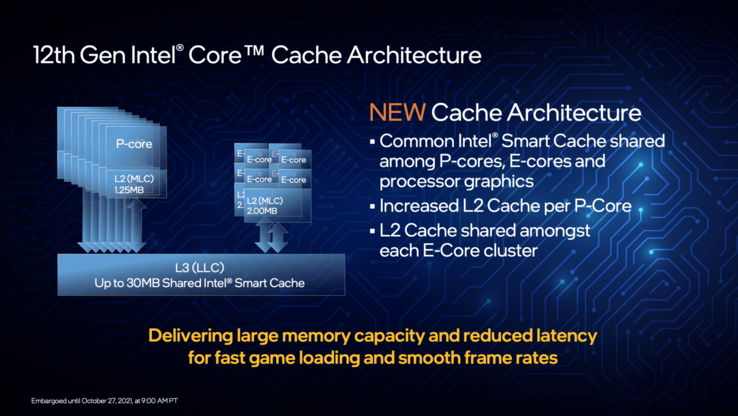

Dato l'uso di due ISA, Intel ha anche rielaborato la topologia della cache per la 12a generazione. L'undicesima generazione Rocket Lake utilizzava i core Cypress Cove, che erano essenzialmente dei Sunny Cove da 10 nm retroportati a 14 nm. Cypress Cove offriva otto core ciascuno con una cache L2 da 512 KB e una cache L3 da 2 MB. Con Alder Lake, ogni P-core ha una cache L2 da 1,25 MB mentre ogni cluster E-core ha una cache L2 condivisa da 2 MB. Pensiamo che questo significhi che un set di quattro E-core condivida una singola cache L2, ma lo confermeremo presto con Intel.

Oltre alle cache L2 dedicate, Alder Lake sfoggia anche una cache L3 condivisa di 30 MB tra entrambi i tipi di core e la GPU integrata per ridurre la latenza. Anche se non è esattamente un confronto alla pari, abbiamo visto come la cache L3 condivisa offre vantaggi immediati in termini di prestazioni nel caso dei processori AMD Ryzen 5000 Zen 3.

Caratteristiche della piattaforma 12th gen - Nessun PCIe Gen5 sul chipset

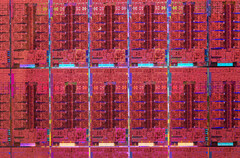

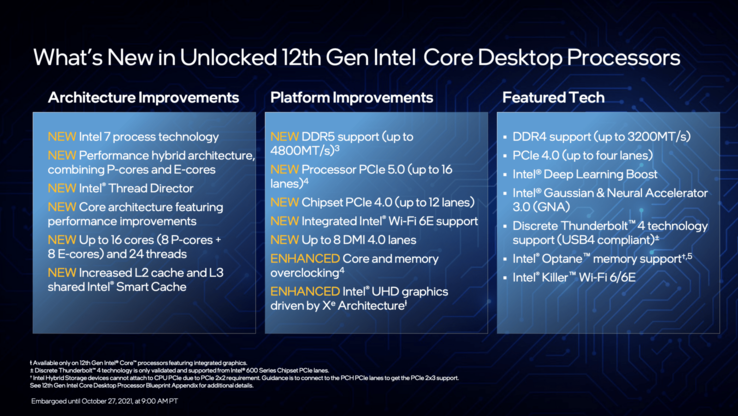

Alder Lake è basato su un processo Enhanced SuperFin a 10 nm, ora noto come Intel 7. Sul desktop, l'ammiraglia Core i9-12900K offrirà fino a 16 core e 24 threads - 8 P-cores che supportano l'hyperthreading e 8 E-cores che non lo fanno.

La CPU supporta la RAM DDR5-4800,e abbiamo anche visto vari annunci di kit DDR5 da parte degli OEM. Detto questo, anche la memoria DDR4-3200 funziona bene

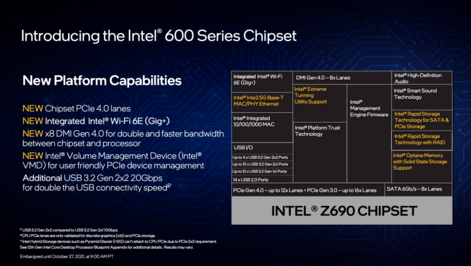

I processori Alder Lake offrono anche fino a 16 corsie di connettività PCIe Gen5. Tuttavia, i chipset della serie 600 possono supportare solo fino a 12 corsie di PCIe Gen4. Le ragioni esatte del taglio su PCIe Gen5 per i chipset della serie 600, compreso il chipset Z690 di punta, non è del tutto chiaro. Potrebbe essere che Intel abbia pensato che una tale implementazione avrebbe fatto salire i prezzi, per non parlare del consumo energetico

Inoltre, anche una GPU come la NVIDIA GeForce RTX 3090 difficilmente può saturare PCIe Gen3 x16. Detto questo, lo storage è un buon beneficiario dell'aumento dell'I/O, quindi potremmo vedere alcune nuove unità NVMe che possono eventualmente utilizzare una buona quantità di larghezza di banda, che nel caso vi stiate chiedendo è circa 128 GB/s aggregati su 16 corsie.

In totale, il chipset Z690 può offrire fino a 28 corsie PCIe - 16 Gen3 e 12 Gen4. Oltre a queste, ci sono otto corsie per Direct Media Interface (DMI) 4.0. Per chi non lo sapesse, DMI è un termine di fantasia per il collegamento tra il processore e il platform controller hub (PCH), ovvero il chipset (Northbridge e Southbridge, nessuno?)

C'è anche il supporto per fino a 4x USB 3.2 Gen2x2, 10x USB 3.2 Gen2, 10x USB 3.2 Gen1, e 14 porte USB 2.0, quindi la connettività non dovrebbe essere un problema. Infine, ci sono otto corsie di porte SATA 6 Gb/s per l'espansione dello storage

Fonte(i)

Breve stampa di Intel