E se il suo disco rigido potesse pensare con i suoi dati? Invece di limitarsi ad archiviare i file, immagina che elabori e risponda alle informazioni esattamente dove sono conservate. Questo è il principio alla base dell'informatica in-memory - un cambiamento crescente nell'architettura che avvicina la logica alla memoria per aumentare l'efficienza.

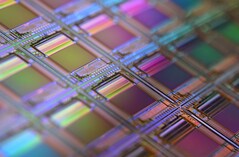

Ora, i ricercatori del Forschungszentrum Jülich e dell'Università di Duisburg-Essen hanno presentato un nuovo design basato su memristori 2T1R che potrebbe supportare questo cambiamento, consentendo un'intelligenza artificiale e un hardware edge più efficienti dal punto di vista energetico.

Pubblicato su arXivil progetto integra due transistor e un memristor per cella, con una regolazione della corrente volta a sopprimere le correnti di percorso, una sfida nota negli array di memristor. A differenza della memoria convenzionale, il design proposto mette a terra entrambi i terminali dei memristori quando sono inattivi - una strategia che può contribuire a migliorare la stabilità del segnale e a ridurre le perdite.

L'architettura è progettata per supportare la moltiplicazione analogica vettore-matrice (VMM), una funzione fondamentale nell'apprendimento automatico, controllando la conduttanza dei memristori mediante DAC integrati, segnali PWM e percorsi di corrente regolati. Un array di prova 2×2 è stato implementato con successo utilizzando la tecnologia CMOS standard a 28 nm.

Affrontando i problemi di terra virtuale e gli effetti di resistenza dei fili, l'architettura mira a migliorare la prevedibilità delle prestazioni e a ridurre il consumo energetico. Con la compatibilità per il controllo RISC-V e l'interfaccia digitale, il progetto 2T1R può gettare le basi per chip neuromorfici scalabili, consentendo un'accelerazione AI più veloce e compatta direttamente nella memoria.

Sebbene il suo disco rigido non stia ancora pensando, l'architettura alla base di questa visione sta già prendendo forma nel silicio, lasciando intendere un futuro di IA più veloce e integrata nella memoria.

Per tutti i dettagli tecnici e i risultati, consulti il preprint arXiv completo (PDF).

Fonte(i)

I nostri Top 10

» Top 10 Portatili Multimedia

» Top 10 Portatili Gaming

» Top 10 Portatili Gaming Leggeri

» Top 10 Portatili da Ufficio e Business economici

» Top 10 Portatili Premium da Ufficio/Business

» Top 10 Portatili sotto i 300 Euro

» Top 10 Portatili sotto i 500 Euro

» Top 10 dei Portatili Workstation

» Top 10 Subnotebooks

» Top 10 Ultrabooks

» Top 10 Convertibili

» Top 10 Tablets

» Top 10 Tablets Windows

» Top 10 Smartphones