Il salto a Zen 4 non avverrà quest'anno, ma AMD ha già una risposta per Intel Alder Lake piattaforma di Intel. Come annunciato al Computex all'inizio di questa estate, AMD aggiornerà i suoi processori Zen 3 con la 3D V-Cache all'inizio del 2022, e questo dovrebbe essere sufficiente per pareggiare il campo di gioco contro Intel, almeno fino al lancio della prossima generazione alla fine del 2022. Al simposio annuale Hot Chips, AMD ha recentemente fornito maggiori dettagli su come funziona la 3D V-Cache e ha anche offerto un'anteprima per le sue future applicazioni di stacking 3D.

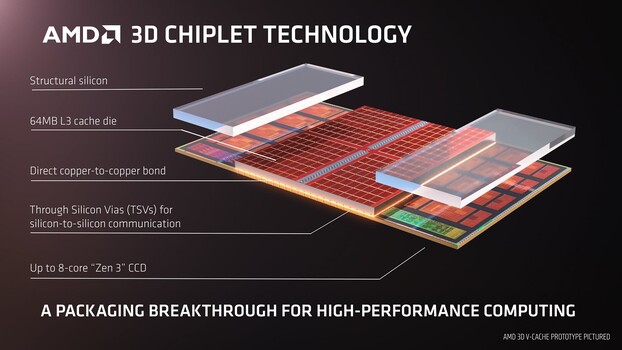

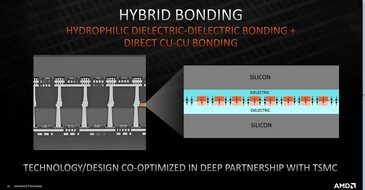

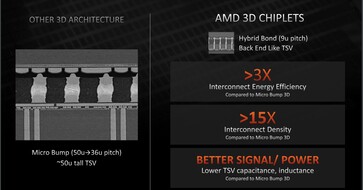

AMD sta implementando un pacchetto di chiplet Micro Bump 3D da 9 micron per la V-Cache attraverso il silicio via (TSV). Anche se solo 1 micron più sottile di quello di Intel Foveros 3D che sarà utilizzato per produrre i processori Alder Lake, i Micro Bump di AMD si dice che offrano più di 3 volte l'efficienza energetica di interconnessione, 15 volte la densità di interconnessione e la capacità/induttanza. L'attuale tecnologia TSV che funge da connessione verticale inter-wafer o inter-die non offre troppi legami, ma, in futuro, il passo TSV diventerà sempre più raffinato, permettendo disegni di impilamento 3D più complessi. V-Cache, per esempio, permette una comunicazione completa da silicio a silicio (DRAM su CPU / CPU su CPU) tramite legami diretti rame-rame. Questo permette l'aggiunta di 64 MB di cache L3 alla quantità esistente, che dovrebbe fornire un aumento delle prestazioni del 15% nei giochi e del 19% nelle applicazioni di creazione di contenuti.

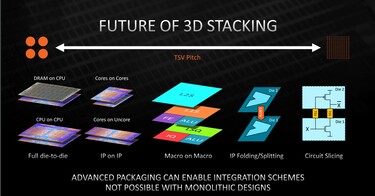

Piazzole TSV più fini permetteranno complesse tecniche di impilamento 3D tra cui IP su IP (core su core / core su uncore), macro su macro (SoC su SoC), e alla fine anche IP folding / splitting e circuit slicing. Anche i requisiti di potenza diminuiranno di più di 3 volte. Probabilmente vedremo la prima applicazione della tecnica IP on IP con i RDNA2 GPU cores impilati sopra i core Zen 4

Leaked AMD documents confirm integrated GPUs for next-generation Socket AM5 processors

I nostri Top 10

» Top 10 Portatili Multimedia

» Top 10 Portatili Gaming

» Top 10 Portatili Gaming Leggeri

» Top 10 Portatili da Ufficio e Business economici

» Top 10 Portatili Premium da Ufficio/Business

» Top 10 Portatili sotto i 300 Euro

» Top 10 Portatili sotto i 500 Euro

» Top 10 dei Portatili Workstation

» Top 10 Subnotebooks

» Top 10 Ultrabooks

» Top 10 Convertibili

» Top 10 Tablets

» Top 10 Tablets Windows

» Top 10 Smartphones